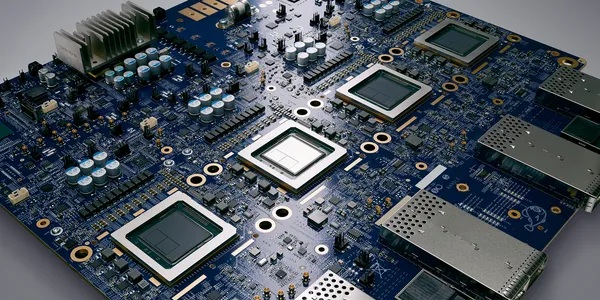

[비즈니스포스트] 삼성전자가 4나노 파운드리 공정에서 대만 TSMC의 수율(완제품 가운데 양품 비율)을 따라잡았다는 주장이 나왔다.

![IT정보유출자, 애플 녹취 인용해 "삼성전자 4나노 수율 TSMC와 비슷"]()

IT정보유출자(팁스터) 레베그너스(Revegnus)는 17일 트위터에 “애플 경영진 회의 녹취록에 따르면 4나노에서 삼성전자와 TSMC의 수율이 거의 같을 것으로 추정된다”고 말했다.

▲ 삼성전자가 4나노 공정에서 수율을 크게 끌어올려 비슷한 수준까지 확보하면서 대만 TSMC를 바짝 추격하고 있는 것으로 파악된다.

또한 레베그너스는 TSMC의 3나노 공정 수율과 관련해 최대 63% 수준인 것으로 추정된다고 전했다.

레베그너스는 TSMC의 3나노 공정 가격이 4나노 공정과 비교해 2배가 되었다는 점도 알렸다.

삼성전자는 4나노 공정이 핀펫(FinFET) 기반의 SF4E(4LPE)로 시작해 SF4(4LPP)를 거쳐 현재 3세대인 SF4P(4LPP+) 버전까지 나온 것으로 알려졌다.

처음 버전에서는 낮은 수율로 어려움을 겪었지만 올해 새로운 3세대 버전에서 급격한 수율 개선을 이룬 것으로 전해진다.

삼성전자는 현재 3나노 공정에서 세계 최초로 차세대 트랜지스터 구조인 게이트올어라운드(GAA)기술을 활용해 양산에 돌입하고 있다.

GAA는 기존 핀펫 구조와 비교해 공정 미세화에 따른 트랜지스터의 성능 저하를 해결하고 데이터 처리 속도 및 전력 효율을 높일 수 있어 촉망받는 반도체 핵심 기술로 거론된다. 조장우 기자