TSMC가 최첨단 3나노 공정에서 수율(결함이 없는 합격품의 비율) 확보에 어려움을 겪으면서 삼성전자가 반사이익을 얻을 수 있다는 시선이 나온다.

해외 IT매체 탐스하드웨어는 21일 반도체업계 소식통을 인용해 "TSMC가 3나노 공정 수율에 어려움을 겪고 있는 것으로 알려졌다”며 “TSMC의 3나노 수율 문제로 고객사인 AMD의 새로운 중앙처리장치(CPU) 개발 계획이 차질을 빚을 수 있다”고 보도했다.

![TSMC 최첨단공정 수율 문제로 어려움 겪어, 삼성전자 반사이익 얻나]()

TSMC와 삼성전자는 모두 올해 3나노 공정을 상용화할 것으로 예상된다.

삼성전자는 3나노 공정 기반의 반도체 양산을 2022년 상반기 안에 시작하겠다는 계획을 세웠다. TSMC는 올해 하반기에 3나노 공정으로 반도체를 양산하겠다고 밝혔다.

하지만 TSMC는 최근 기존 ‘핀펫(FinFET)’’ 방식의 3나노 공정으로는 만족스러운 수율을 달성하기가 매우 어렵다는 것을 절감한 것으로 알려졌다.

반면 삼성전자는 트랜지스터의 채널과 게이트가 4면에서 맞닿게 하는 ‘게이트올어라운드(GAA)’ 방식을 3나노에 새롭게 도입해 TSMC와 차별화된 전략을 추진하고 있다.

게이트올어라운드는 채널과 게이트 접촉면이 3면에 그치는 핀펫 방식보다 반도체가 동작하는 전압을 낮추고 성능을 개선할 수 있는 방식이다.

AMD는 애초 TSMC의 3나노 방식으로 차세대 CPU ‘ZEN5’와 그래픽처리장치(GPU) ‘RDNA4’를 개발한다는 방침을 세운 것으로 전해진다. 하지만 TSMC가 수율 문제를 해결하지 못한다면 5나노 공정을 사용하거나 삼성전자의 3나노 공정을 검토할 수도 있을 것으로 예상된다.

다만 삼성전자는 4나노 공정에서 수율 문제를 겪고 있어 3나노 공정의 수율도 불투명할 것이란 관측이 나오고 있다.

삼성전자는 최근 파운드리사업부의 첫 감사(경영진단)에 착수했다. 감사팀은 선단공정의 낮은 수율 문제를 집중적으로 조사하고 있는 것으로 알려졌다.

탐스하드웨어는 “삼성전자도 3나노 공정에서 중요한 장애물을 넘어야 한다”며 “게이트올어라운드로 변경하는 것은 매우 까다롭지만 이에 성공하면 다음 공정을 더 쉽게 진행할 수 있는 강점이 될 것이다”고 분석했다. [비즈니스포스트 나병현 기자]

해외 IT매체 탐스하드웨어는 21일 반도체업계 소식통을 인용해 "TSMC가 3나노 공정 수율에 어려움을 겪고 있는 것으로 알려졌다”며 “TSMC의 3나노 수율 문제로 고객사인 AMD의 새로운 중앙처리장치(CPU) 개발 계획이 차질을 빚을 수 있다”고 보도했다.

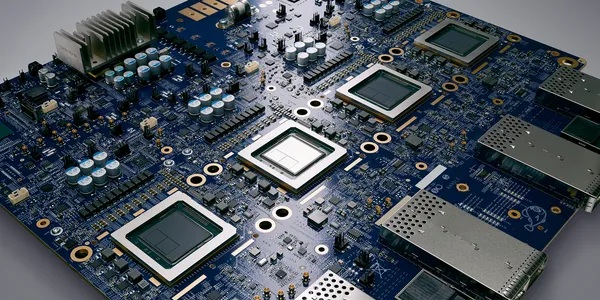

▲ 대만 TSMC의 반도체 위탁생산공장.

TSMC와 삼성전자는 모두 올해 3나노 공정을 상용화할 것으로 예상된다.

삼성전자는 3나노 공정 기반의 반도체 양산을 2022년 상반기 안에 시작하겠다는 계획을 세웠다. TSMC는 올해 하반기에 3나노 공정으로 반도체를 양산하겠다고 밝혔다.

하지만 TSMC는 최근 기존 ‘핀펫(FinFET)’’ 방식의 3나노 공정으로는 만족스러운 수율을 달성하기가 매우 어렵다는 것을 절감한 것으로 알려졌다.

반면 삼성전자는 트랜지스터의 채널과 게이트가 4면에서 맞닿게 하는 ‘게이트올어라운드(GAA)’ 방식을 3나노에 새롭게 도입해 TSMC와 차별화된 전략을 추진하고 있다.

게이트올어라운드는 채널과 게이트 접촉면이 3면에 그치는 핀펫 방식보다 반도체가 동작하는 전압을 낮추고 성능을 개선할 수 있는 방식이다.

AMD는 애초 TSMC의 3나노 방식으로 차세대 CPU ‘ZEN5’와 그래픽처리장치(GPU) ‘RDNA4’를 개발한다는 방침을 세운 것으로 전해진다. 하지만 TSMC가 수율 문제를 해결하지 못한다면 5나노 공정을 사용하거나 삼성전자의 3나노 공정을 검토할 수도 있을 것으로 예상된다.

다만 삼성전자는 4나노 공정에서 수율 문제를 겪고 있어 3나노 공정의 수율도 불투명할 것이란 관측이 나오고 있다.

삼성전자는 최근 파운드리사업부의 첫 감사(경영진단)에 착수했다. 감사팀은 선단공정의 낮은 수율 문제를 집중적으로 조사하고 있는 것으로 알려졌다.

탐스하드웨어는 “삼성전자도 3나노 공정에서 중요한 장애물을 넘어야 한다”며 “게이트올어라운드로 변경하는 것은 매우 까다롭지만 이에 성공하면 다음 공정을 더 쉽게 진행할 수 있는 강점이 될 것이다”고 분석했다. [비즈니스포스트 나병현 기자]