![SK하이닉스 첨단패키징 상용화 서둘러, 메모리 성능과 원가절감 잡아]()

| ▲ SK하이닉스가 팬아웃웨이퍼레벨패키지(FO-WLP) 관련 경력자를 채용하고 있다. < SK하이닉스 채용사이트 갈무리 > |

SK하이닉스가 메모리반도체사업 경쟁력을 키우기 위해 첨단패키징기술 상용화에 속도를 내고 있다.

패키징은 반도체칩을 포장해 제품화하는 공정을 말한다. 수준 높은 패키징기술은 단순히 반도체를 보호할 뿐 아니라 제품 성능을 개선하고 원가 절감을 이루는 데도 기여한다.

26일 SK하이닉스에 따르면 최신 반도체 패키징기술 팬아웃웨이퍼레벨패키지(FO-WLP)기술을 메모리반도체 공정에 적용하기 위해 팬아웃웨이퍼레벨패키지 공정 및 제품 개발을 수행할 경력자 채용절차를 진행하고 있다.

팬아웃웨이퍼레벨패키지는 기존 패키징기술과 비교해 크기 간소화, 성능 향상, 원가 절감 등 여러 면에서 이점이 있다.

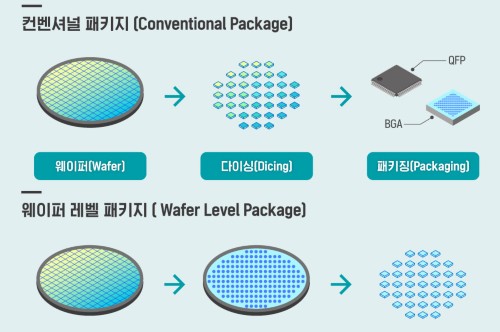

기존 패키징은 웨이퍼에 만들어진 반도체칩을 일일이 잘라내 개별 기판에 올려 연결하는 방식이다. 웨이퍼레벨패키지(WLP)는 이보다 더 발전된 방식으로 팬인웨이퍼레벨패키지(FI-WLP)와 팬아웃웨이퍼레벨패키지 등으로 나뉜다.

팬인웨이퍼레벨패키지(WLP)에서는 기존 패키징 방식과 달리 칩을 잘라내지 않고 원형 웨이퍼 상태 그대로 반도체를 패키징한 뒤 단품으로 분리하게 된다.

칩 크기 그대로 패키징하는 만큼 기존 패키징 방식보다 더 작은 완제품을 구현할 수 있다. 또 기판이나 와이어 같은 부가재료가 따로 필요하지 않기 때문에 생산비용이 적게 든다.

![SK하이닉스 첨단패키징 상용화 서둘러, 메모리 성능과 원가절감 잡아]()

| ▲ 기존 패키징(컨벤셔널 패키지) 방식과 웨이퍼레벨패키지 방식 차이. < SK하이닉스 > |

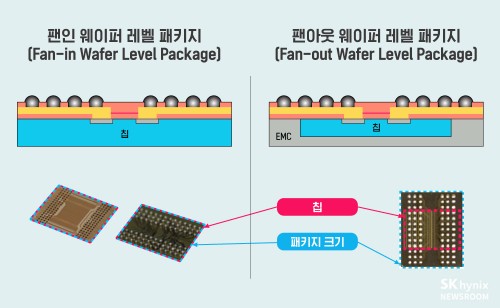

다만 팬인웨이퍼레벨패키지에도 단점은 존재한다. 반도체 입출력단자의 범위가 칩 크기로만 제한돼 데이터 처리속도 등 성능을 높이는 데 제약이 생긴다. 웨이퍼 상태에서 불량이 난 칩을 양품과 함께 패키징해야 하는 것도 문제다.

팬아웃웨이퍼레벨패키지는 팬인웨이퍼레벨패키지의 이런 약점들을 극복하기 위해 개발됐다. 웨이퍼에서 양품인 칩을 골라 잘라낸 뒤 웨이퍼와 같은 원형 판(캐리어)에 새로 올려 패키징하는 방식이 도입된 것이다.

팬아웃웨이퍼레벨패키지를 적용하면 불량품을 선별해 완제품 수율을 개선하는 한편 원하는 대로 패키지 크기를 조절해 입출력단자를 칩 크기보다 더 넓게 배치하는 것이 가능하다.

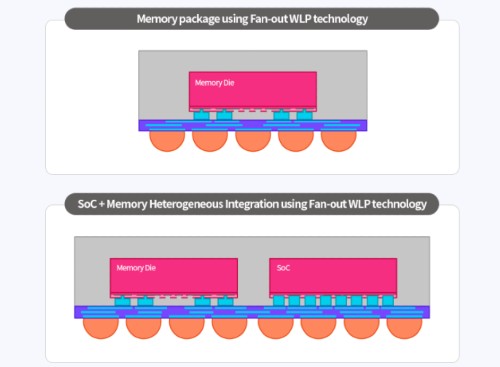

패키지 크기가 조절되는 만큼 메모리반도체와 시스템반도체 등 서로 다른(이기종) 칩을 한 제품으로 패키징하는 데 유리하다는 것도 장점으로 꼽힌다. 이기종 패키징이 적용된 반도체는 각 칩을 따로 패키징해 완제품에 적용하는 것과 비교해 크기가 줄고 데이터 전송속도가 향상된다.

SK하이닉스는 팬아웃웨이퍼레벨패키지 도입을 통해 점점 더 높아지는 고객의 요구를 충족시킬 수 있을 것으로 기대하고 있다.

SK하이닉스는 뉴스룸을 통해 “현재 메모리제품에 팬아웃웨이퍼레벨패키지기술을 활용하는 방안을 검토하고 있다”며 “현재 D램이 가진 성능의 한계를 획기적으로 향상시키는 패키지 구조를 구현하고 메모리와 시스템온칩(SoC) 등 서로 다른 장치의 직접적 패키징기술 개발, 반도체 생태계에서 주도적 참여 등도 가속화할 수 있을 것이다”고 말했다.

![SK하이닉스 첨단패키징 상용화 서둘러, 메모리 성능과 원가절감 잡아]()

| ▲ 팬아웃웨이퍼레벨패키지를 적용한 반도체(오른쪽)는 팬인웨이퍼레벨패키지 기반 제품과 비교해 더 많은 입출력단자를 확보할 수 있다. < SK하이닉스 > |

팬아웃웨이퍼레벨패키지는 기존에는 애플리케이션 프로세서(AP)나 전력관리칩(PMIC) 같은 시스템반도체에 주로 쓰였다. 대만 TSMC와 삼성전자 등이 애플리케이션 프로세서를 통해 상용화한 바 있다.

SK하이닉스가 이 공정을 메모리반도체로 도입하는 이유는 반도체회로 미세화에 따른 성능 개선에 한계가 있기 때문이다.

반도체는 회로폭이 좁아질수록 속도와 전력 효율성 등 성능이 좋아진다. 하지만 최근 들어 회로폭이 나노미터(nm) 단위로 미세화하면서 이보다 더 미세공정을 고도화하는 일이 점점 더 어려워지고 있다.

손호영 SK하이닉스 IIP팀 PL은 21일 기술매체 EE타임스 기고문에서 “반도체 제조가 향후 몇 년 안에 물리적 한계에 직면할 가능성이 높아짐에 따라 패키징 기술이 어느 때보다도 주목받고 있다”며 “팬아웃웨이퍼레벨패키지는 메모리 제품 성능을 개선하면서 새로운 애플리케이션으로 확장을 가능하게 한다”고 말했다.

원가 절감도 팬아웃웨이퍼레벨패키지 도입에 따른 중요한 개선점으로 꼽힌다.

반도체업계에 따르면 팬인웨이퍼레벨패키지를 적용한 반도체는 기존 대비 패키지 생산원가의 약 20%가 절감된다. 팬아웃웨이퍼레벨패키지는 불량품을 패키징하지 않아도 된다는 이점이 더해져 팬인웨이퍼레벨패키지보다도 원가 절감효과가 더 뛰어나다.

SK하이닉스는 현재 팬인웨이퍼레벨패키지 기반으로 고대역폭메모리(HBM)를 양산하고 있다. HBM은 D램 칩을 여러 개 쌓은 제품으로 일반 D램보다 적은 전력을 소모하면서도 더 빠른 속도를 제공한다. 시스템반도체와 함께 탑재돼 한 시스템을 이루는 시스템인패키지(SIP) 형태로 공급된다.

SK하이닉스가 지난해 7월 선보인 HBM2E의 경우 팬인웨이퍼레벨패키지를 적용해 기존 패키징 방식이 쓰인 제품보다 크기는 30% 이상, 전력 소모는 50% 이상 감소했다.

SK하이닉스가 팬인웨이퍼레벨패키지보다 더 발달된 팬아웃웨이퍼레벨패키지를 향후 상용화하면 HBM과 같은 고부가 메모리반도체 제품의 경쟁력을 더욱 높일 수 있을 것으로 전망된다.

손윤철 조선대 용접·접합과학공학과 교수는 팬아웃웨이퍼레벌패키지 기술 동향’ 논문을 통해 “팬아웃웨이퍼레벨패키지는 기존 패키지 대비 칩 크기를 16분의1 정도 수준으로 줄일 수 있고 인쇄회로기판을 사용하지 않아 원가 경쟁력이 높다”며 “또 한 패키지에 다양한 기능의 칩들을 심는 시스템인패키지가 가능해 빠르게 변하는 모바일기기와 사물인터넷시장에서 매우 유리한 패키징기술이다”고 말했다. [비즈니스포스트 임한솔 기자]

![SK하이닉스 첨단패키징 상용화 서둘러, 메모리 성능과 원가절감 잡아]()

| ▲ 팬아웃웨이퍼레벨패키지 기반 메모리반도체(위쪽)와 메모리 및 시스템반도체 결합 제품. < SK하이닉스, EE타임스 > |