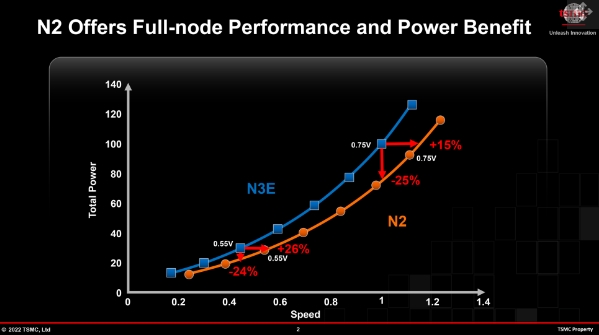

▲ TSMC의 2나노 공정과 3나노(N3E)의 속도 및 전성비 차이. < TSMC >

TSMC는 현지시각 16일 미국 실리콘밸리에서 열린 기술 심포지엄에서 이를 내용을 포함해 2025년 양산을 목표로 개발하고 있는 2나노 공정기술 특징에 관해 설명했다.

TSMC가 2나노 칩 생산 일정을 구체적으로 확정한 것은 이번이 처음이다.

TSMC는 나노시트를 바탕으로 한 트랜지스터 생산 신기술인 ‘게이트올어라운드(GAAFET)’ 방식을 2나노 공정에 처음 적용해 반도체 작동 속도와 전력 효율성을 극대화한다.

반도체 구성 단위인 트랜지스터는 전류가 흐르는 '채널'과 채널을 제어하는 ‘게이트’로 이뤄진다. 게이트올어라운드는 트랜지스터의 채널과 게이트가 4면에서 맞닿게 하는 기술이다.

채널과 게이트 접촉면이 3면에 그치는 기존 ‘핀펫(FinFET)’ 방식보다 반도체가 동작하는 전압을 낮추고 성능을 개선할 수 있다.

삼성전자는 TSMC와 달리 올해 상용화할 3나노 공정부터 게이트올어라운드 방식을 도입한다.

삼성전자도 2025년 2나노 공정에 들어간다는 계획을 세우고 있다.

TSMC는 새로운 트렌지스터 생산 방식을 적용한 2나노 공정이 3나노(N3E) 대비 속도는 10~15% 빨라지고 전성비는 25~30% 개선될 것으로 보고 있다.

다만 2나노 공정은 집적도 측면에서 향상이 크지 않을 것으로 예상된다.

그동안 반도체 업계는 미세화를 통해 트랜지스터 회로의 집적도를 높이는 데 주력해왔다. 반도체 집적도가 높아지면 소비 전력이 줄어들고 동작 속도가 빨라지는 장점이 있기 때문이다.

반도체업계에는 그동안 2년마다 반도체 칩의 미세소자 집적도가 2배씩 증가한다는 ‘무어의 법칙’이 존재했다.

하지만 측정 단위가 사람 머리카락 두께의 5만분의 1 수준인 나노까지 작아지면서 사실상 무어의 법칙은 한계에 이르렀다.

이에 따라 기업들은 집적도 향상의 한계를 극복하기 위해 트랜지스터 구성 방식의 변화를 통해 성능을 개선하고 있다.

TSMC의 2나노 공정은 3나노(N3E)보다 집적도가 1.1배 개선되는 데 그칠 것으로 예상되고 있다.

해외 IT매체 톰스하드웨어는 “TSMC의 새로운 2나노 공정은 성능과 전성비 등에서 상당한 이점을 제공할 것으로 기대된다”며 “다만 트랜지스터 밀도와 관련해서는 거의 감명을 주지 못할 것”이라고 평가했다. 나병현 기자

![[코스피 5천 그늘①] 증시 활황에도 못 웃는 LG그룹, 구광모 '체질 개선'과 '밸류업'으로 저평가 끊나](https://businesspost.co.kr/news/photo/202602/20260209151542_142553.jpg)

![[코스피 5천 그늘②] 롯데그룹 주주 흥 돋는 카드 안 보인다, 신동빈 유통·화학 계열사 '시장 소외'에 속앓이](https://businesspost.co.kr/news/photo/202601/P_20260127151310_76677.jpg)